Design a digital system whose output is defined as logically low. If the 4 bit inpur binary number is a multiple of 3. Otherwise, the output will be logically high. The output is defined if and only if the input binary number is greater than 2

Design of a Digital System for Multiples of 3 Detection

Problem Statement:

We need to design a digital system that outputs a logically low (0) when a 4-bit input binary number is a multiple of 3. Otherwise, the output should be logically high (1). Additionally, the output should only be defined if the input number is greater than 2.

Step 1: Identifying Multiples of 3 in 4-bit Binary

A 4-bit binary input ranges from 0000 (0) to 1111 (15). However, we only consider numbers greater than 2 (i.e., from 3 to 15). The multiples of 3 in this range are:

- 3 (0011)

- 6 (0110)

- 9 (1001)

- 12 (1100)

- 15 (1111)

For these inputs, the output should be low (0). For all other numbers, the output should be high (1).

Step 2: Karnaugh Map (K-Map) for Optimization

Using a 4-variable Karnaugh map (K-map), we map the outputs for inputs 3 to 15.

| AB/CD | 00 | 01 | 10 | 11 |

|---|---|---|---|---|

| 00 | X | X | 1 | 0 |

| 01 | 1 | 0 | 1 | 1 |

| 10 | 0 | 1 | 1 | X |

| 11 | 0 | X | X | X |

Where X indicates an undefined condition (input < 3).

The minimized Boolean equation for the output (Y) is:

[

Y = \overline{(A \oplus B)C + \overline{B}D}

]

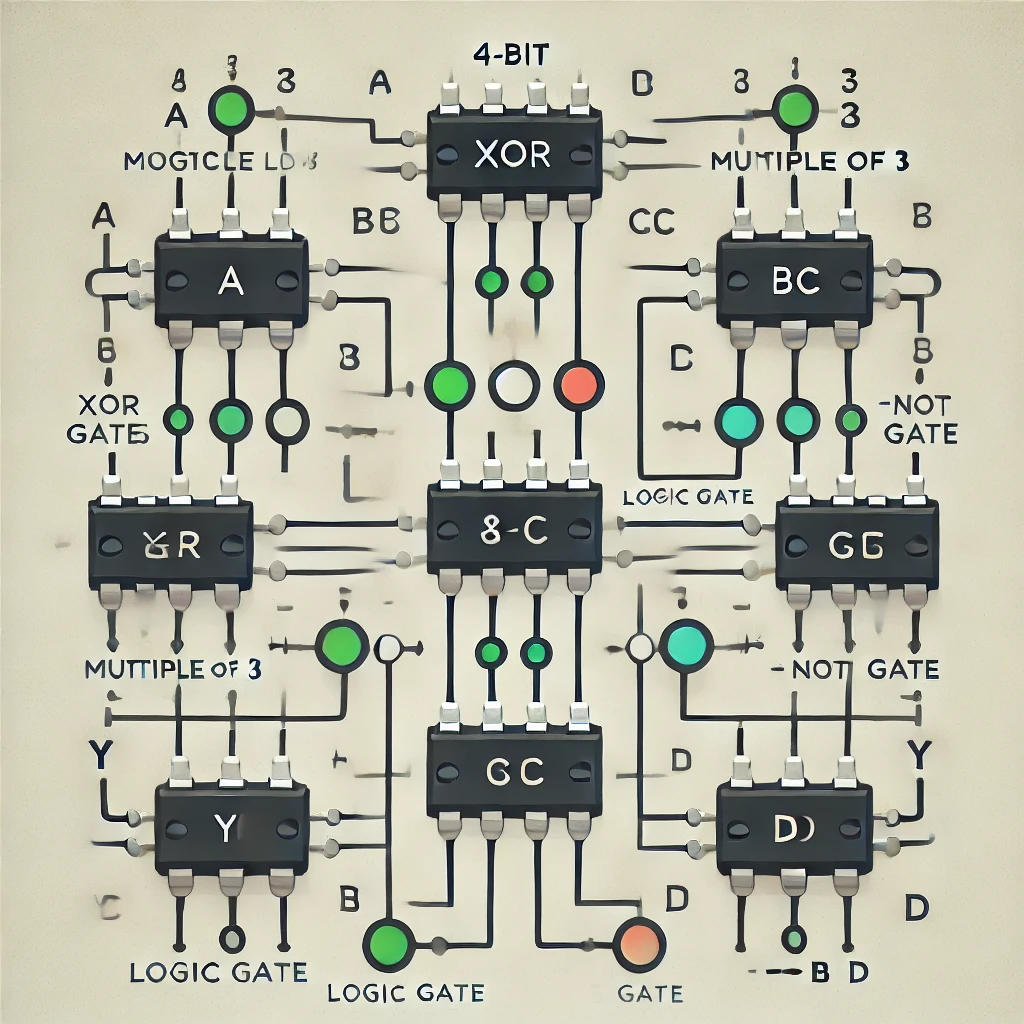

Step 3: Logic Circuit Design

Using the equation derived, the digital system can be designed using XOR gates, AND gates, and NOT gates.

Final Design

- Input: 4-bit binary (A, B, C, D)

- Output: Y (0 if multiple of 3, 1 otherwise)

- Components Used: XOR gates, AND gates, NOT gates

Here is the digital logic circuit diagram that detects multiples of 3 for a 4-bit binary input. The circuit follows the equation:

[

Y = \overline{(A \oplus B)C + \overline{B}D}

]

The output is logically low (0) when the input is a multiple of 3 and logically high (1) otherwise.